深入分析AXI4总线协议的实现细节,包括突发传输、WLAST信号处理、SDRAM接口等关键问题的解决方案。

wlast

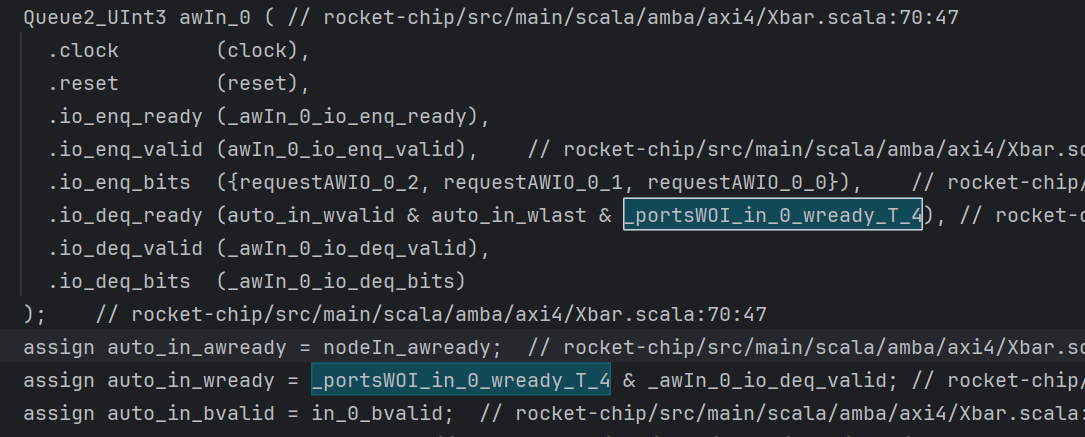

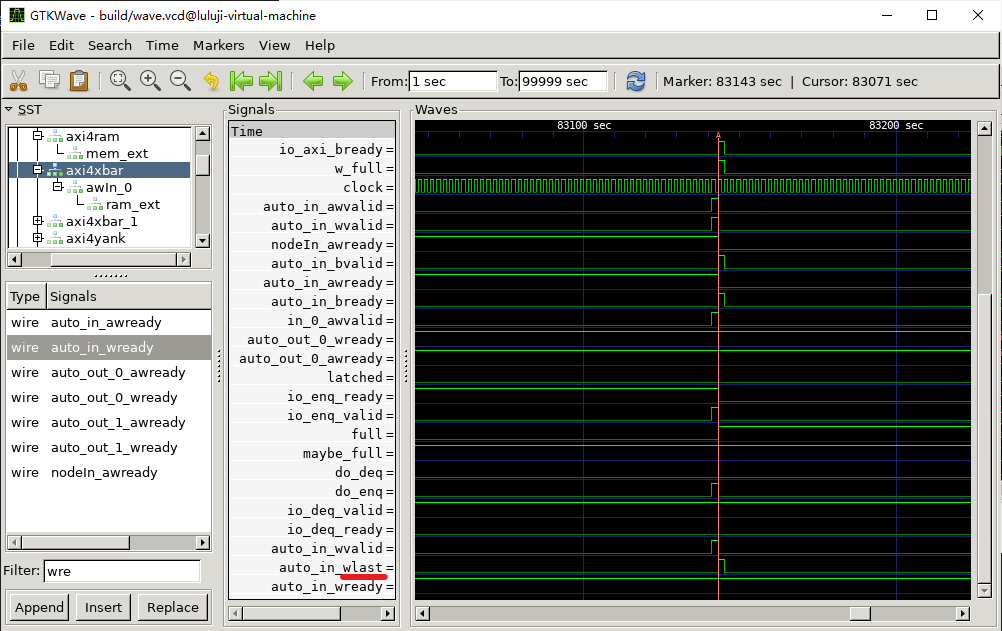

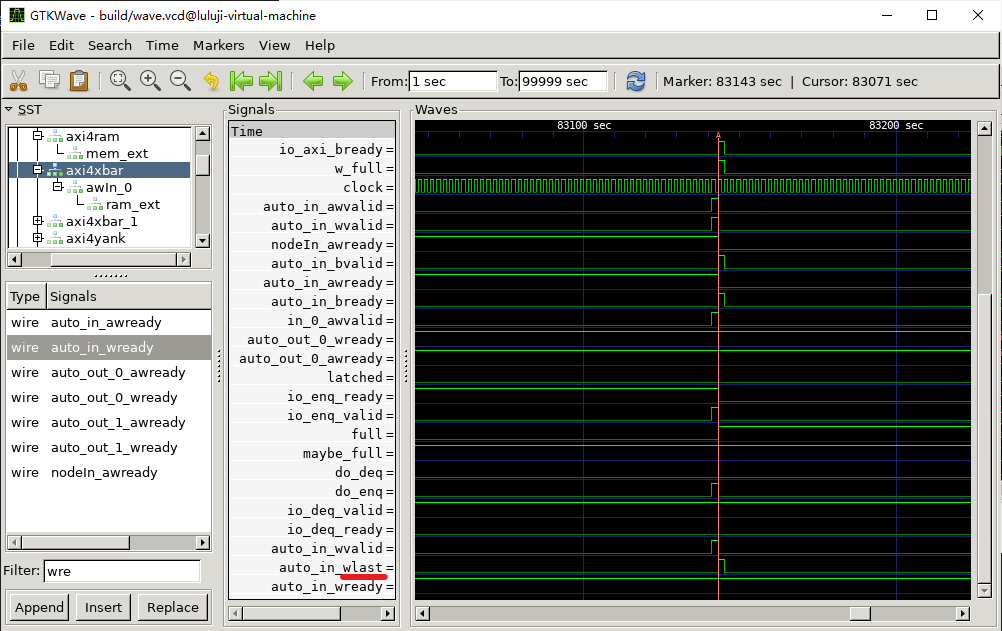

使用sdram-axi后,写入flash出现的问题。xbar的auto_in没问题,但in_0的awvalid没有置1

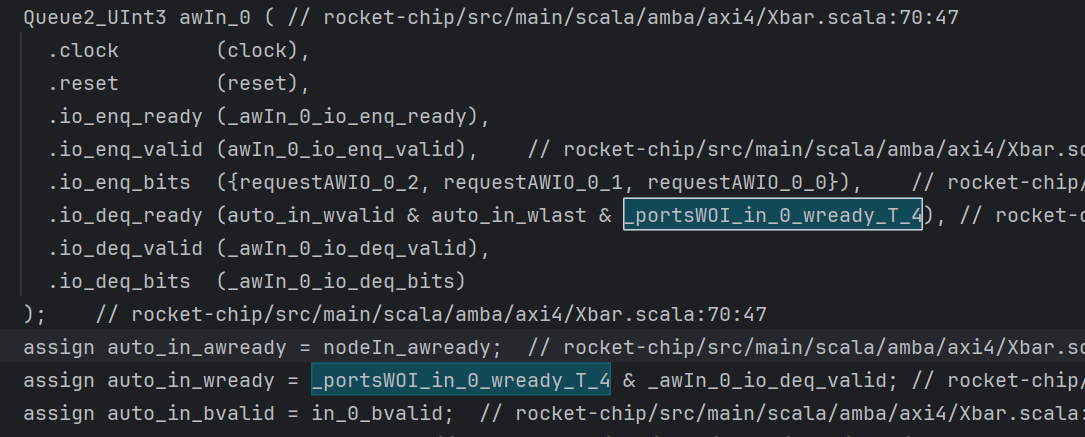

用到了队列,但io_deq_ready一直没有激活,一直无法从队列中弹出第一次axi事务的信号。

原因是wlast用于指示最后一个axi的transfer.如果只有一个transfer,那wlast要和wvalid同时为1

加上提前wlast的信号

1 | when(idx_beat === num_beats(lenReg) -1.U){ |

突发传输

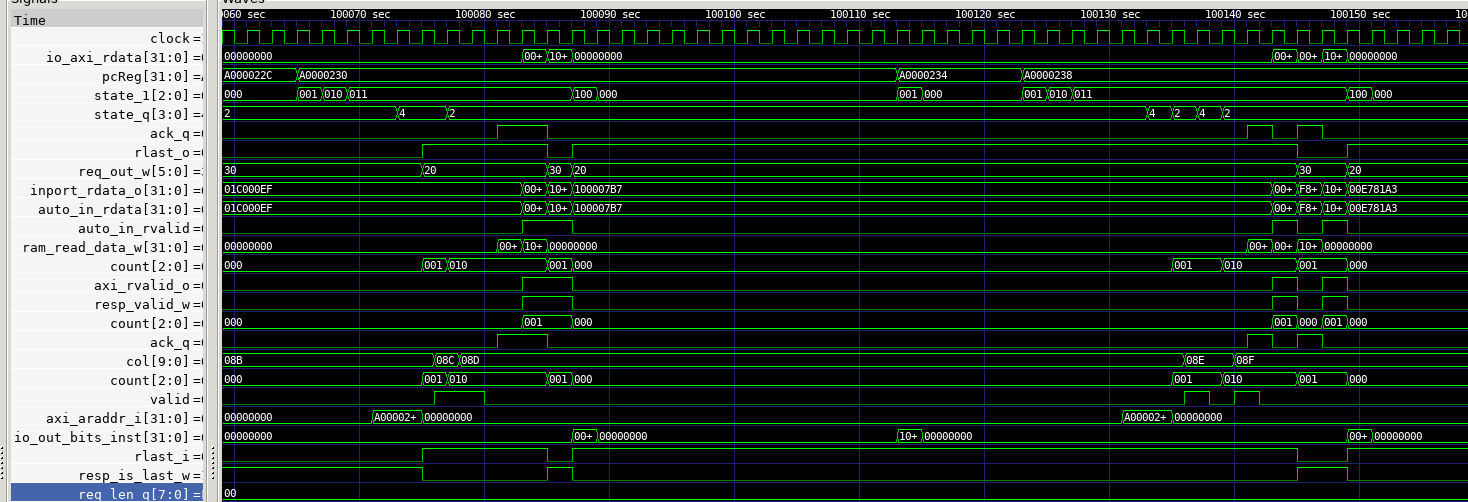

一次事务的结束以rlast/wlast为标志,cpu中xbar和arbiter要做修改,在收到rlast/wlast时切换道空闲状态。否则cpu中总线收不到rlast/wlast

写的信号关系

1.master的wvalid不能依赖awready

sdram的突发

assign wlast_o = axi_wlast_i;

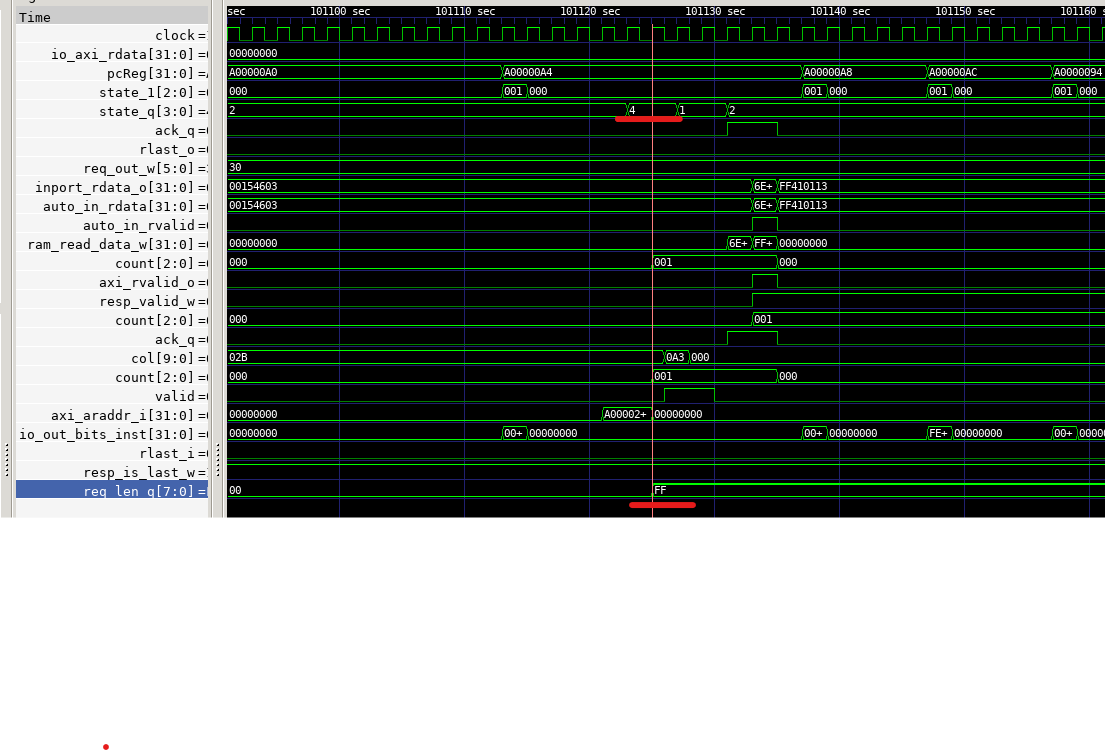

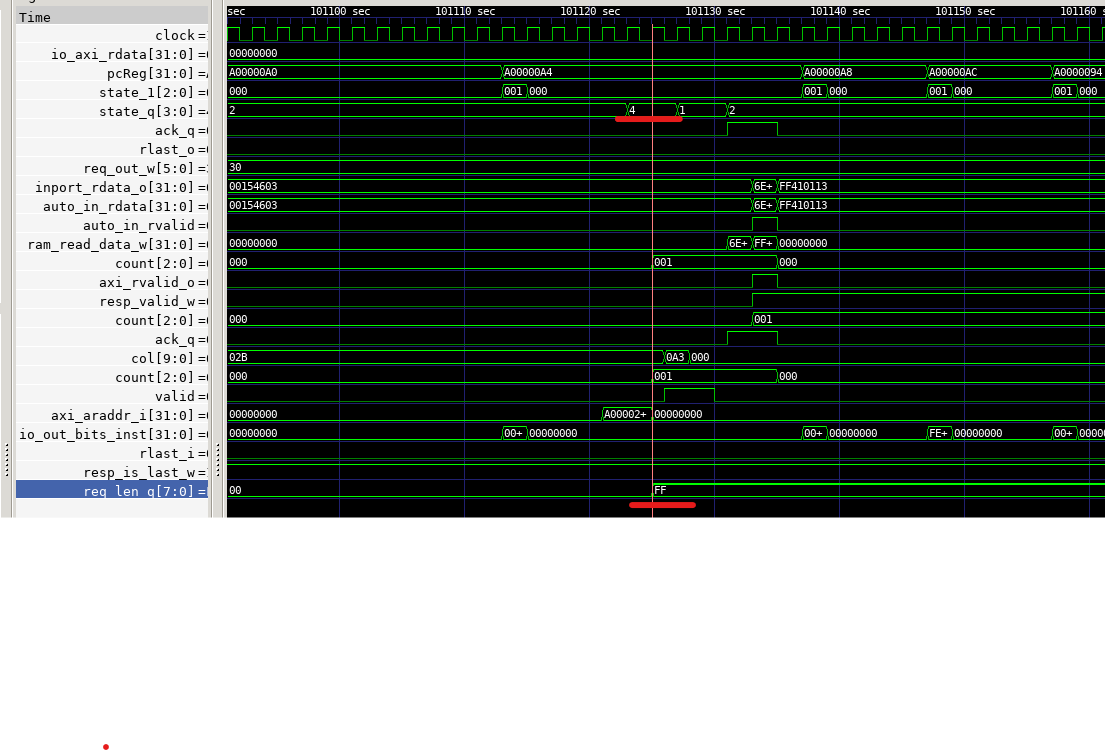

assign rlast_o = !resp_is_last_w | axi_arlen_i==8’d0;

下图的state_q应该只用一个周期。一个周期后req_len_q==ff,晚了一个周期。因此只能使用axi_arlen_i

突发成功了和突发没成功