详细介绍指令缓存(ICache)的实现方法和优化策略,包括多路组相联、替换策略、突发传输等配置的影响分析。

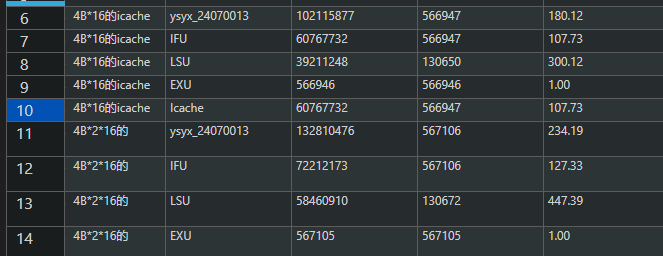

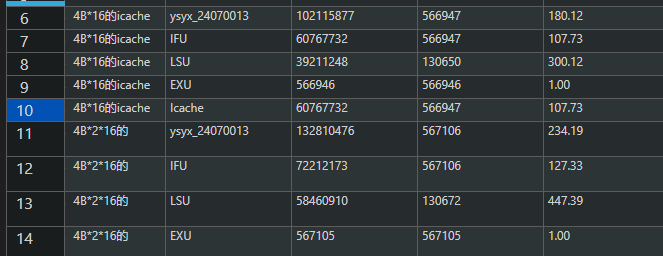

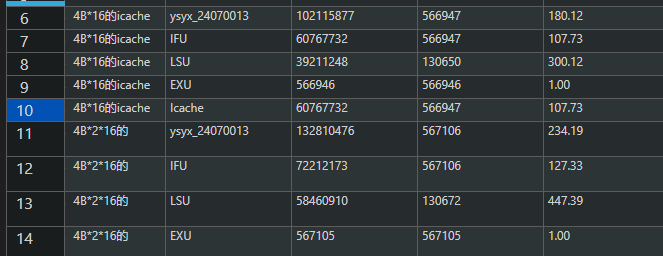

变成两路后好像负优化了

Icache配置切换

1

2

3

4

5

6

7

8

| trait IcacheConfig{

val BlockSize: Int = 8

val WayNum : Int = 1

val SetNum: Int = 16

val Strategy: String = "RANDOM"

val burst: String = "INCR"

}

|

Icache的控制参数

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

| wire _GEN = state == 3'h0;

wire _GEN_0 = state == 3'h1;

wire [7:0] _GEN_1 = {5'h0, sizeReg};

wire _GEN_2 = _GEN | ~_GEN_0;

wire _GEN_3 = state == 3'h2;

wire _GEN_4 = _GEN | _GEN_0;

wire io_axi_wvalid_0 = ~_GEN_4 & _GEN_3;

wire [7:0] _wstrbReg_T = 8'h1 << _GEN_1;

wire _GEN_5 = _GEN_4 | ~_GEN_3;

wire _GEN_6 = idx_beat == lenReg;

wire _GEN_7 = io_axi_awready & io_axi_wready;

wire _GEN_8 = state == 3'h3;

wire _GEN_9 = _GEN | _GEN_0 | _GEN_3;

wire _GEN_10 = _GEN_8 & io_axi_rvalid;

wire _GEN_11 = io_axi_rlast | _GEN_6;

wire _GEN_12 = state == 3'h4;

wire _GEN_13 = _GEN_8 | ~_GEN_12;

|